Figure

Description

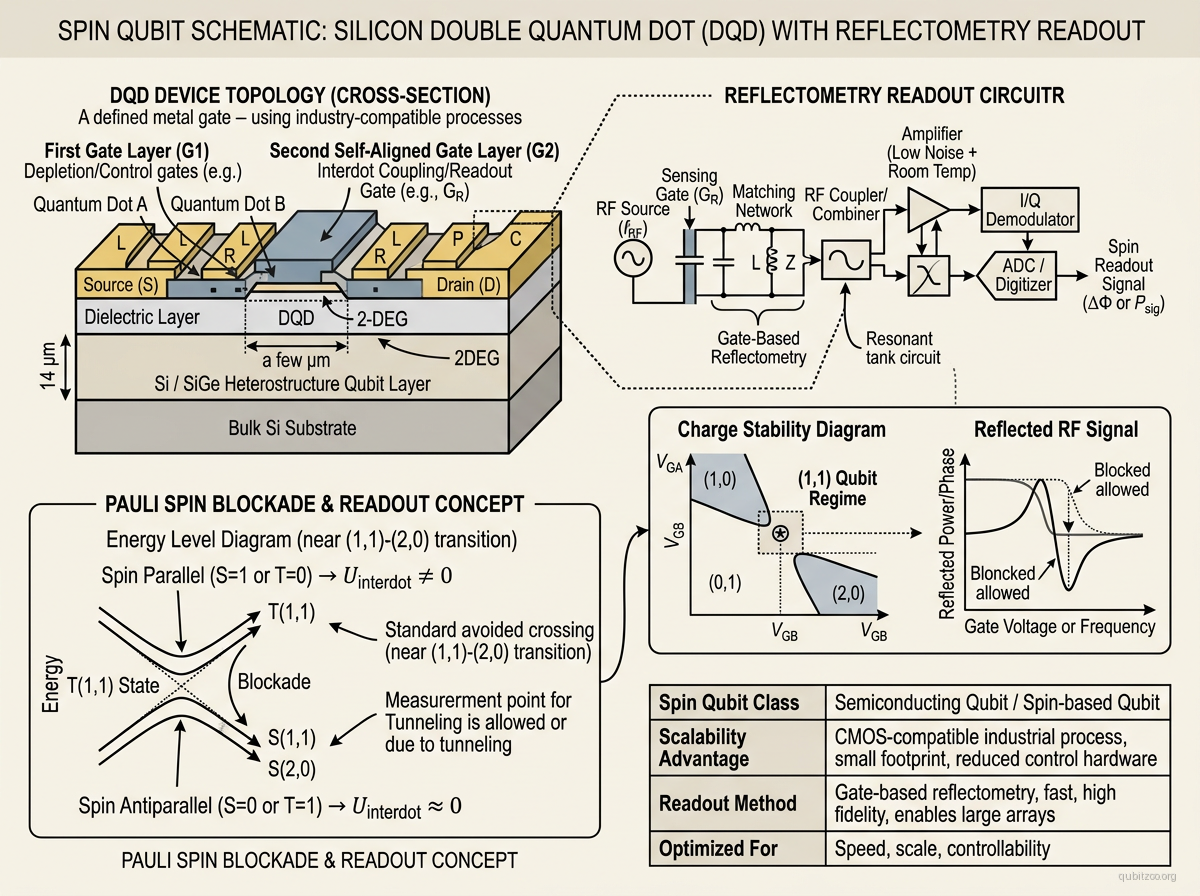

The semiconductor spin qubit, proposed by Loss and DiVincenzo in 1998, encodes quantum information in the spin state of a single electron (or hole) confined in a gate-defined quantum dot. The qubit states are the spin-up and spin-down states of the electron, split by the Zeeman energy in an applied magnetic field.

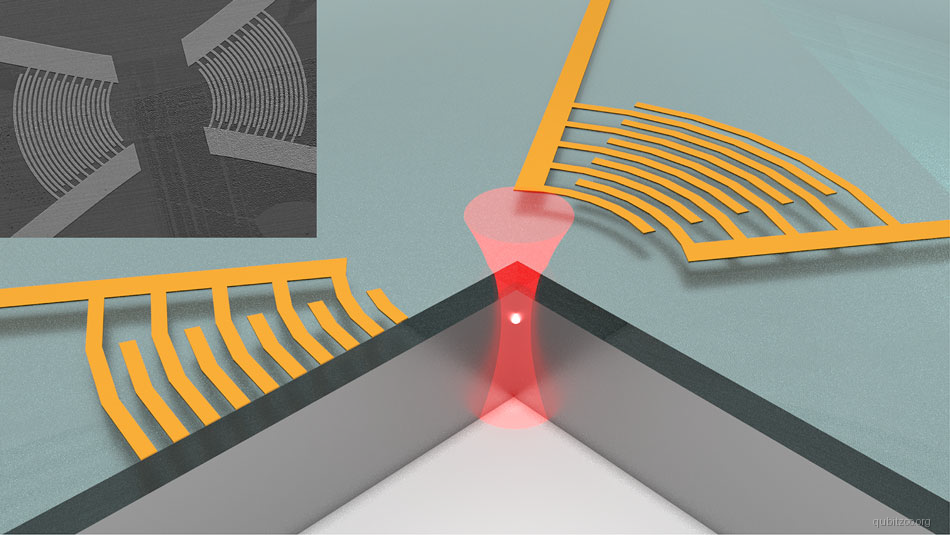

Single-qubit gates are performed via electron spin resonance (ESR) — applying an oscillating magnetic field at the Larmor frequency — or, more commonly in modern implementations, via electric-dipole spin resonance (EDSR), which uses an oscillating electric field combined with spin-orbit coupling or a micromagnet field gradient to drive spin rotations electrically. Electric driving is strongly preferred because it can be delivered through existing gate electrodes and is far easier to localize to individual qubits.

Two-qubit gates exploit the Heisenberg exchange interaction between neighboring dots, controlled by the tunnel barrier gate voltage. A gate — the exchange interaction applied for a calibrated duration — is a universal two-qubit entangling gate.

The major materials platforms are:

- Si/SiGe heterostructures: lower spin-orbit coupling, longer , isotopic purification () removes nuclear spin noise.

- Si MOS (metal-oxide-semiconductor): CMOS-compatible fabrication, sharp interfaces.

- Ge/SiGe hole spin qubits: strong spin-orbit coupling enables all-electric control without micromagnets, but shorter coherence.

- GaAs: historically first demonstrations, but nuclear spin bath limits to ~μs without dynamical decoupling.

Hamiltonian

Single spin in a magnetic field with exchange coupling to a neighbor:

where is the electron -factor, is the Bohr magneton, is the applied field, and is the exchange coupling controlled by the inter-dot barrier gate voltage:

with the tunnel coupling and the on-site Coulomb repulsion. In the Hubbard model limit, the two-electron, two-dot Hamiltonian is:

Motivation

Semiconductor spin qubits promise integration with existing CMOS fabrication infrastructure, enabling potential scaling to millions of qubits using industrial foundry processes. The electron spin is naturally a two-level system with weak coupling to the solid-state environment (especially in isotopically purified , where the nuclear spin bath is eliminated). Qubit pitches of are orders of magnitude smaller than superconducting or trapped-ion qubits.

Experimental Status

Original proposal — Loss and DiVincenzo (1998):

- Proposed single-spin qubits in gate-defined quantum dots with exchange-based two-qubit gates

- Established the foundational architecture for semiconductor quantum computing

Isotopic purification breakthrough:

- Isotopic purification of silicon () eliminates hyperfine decoherence, achieving

Single-qubit gate fidelities — Yoneda et al. (2018):

- Single-qubit gate fidelities demonstrated in quantum dots

- Coherence limited by charge noise, not magnetic noise

Two-qubit gate fidelities (2022):

- Noiri et al. (2022): Fast universal quantum gate above the fault-tolerance threshold in silicon, two-qubit fidelity

- Xue et al. (2022): Quantum logic with spin qubits crossing the surface code threshold

- Mills et al. (2022): Two-qubit silicon quantum processor with operation fidelity exceeding 99%

Multi-qubit processors — Philips et al. (2022):

- Universal control of a six-qubit quantum processor in silicon

- Demonstrated all-to-all connectivity within the six-qubit register

Error correction milestone (2024):

- Above-threshold quantum error correction demonstrated in spin qubits

CMOS compatibility:

- CMOS-compatible fabrication demonstrated at Intel, imec, and CEA-Leti

Key Metrics

| Metric | Value | Notes | Fidelity reference |

|---|---|---|---|

| 1–50 s | Spin relaxation in Si at ~100 mK | Zwanenburg et al. 2013 | |

| 1–120 μs | Si; GaAs ~10 ns without echo | — | |

| (echo) | 1–28 ms | Si with Hahn echo | — |

| 1Q gate fidelity | 99.9–99.96% | Si, randomized benchmarking | Yoneda et al. 2018 |

| 2Q gate fidelity | 99.5–99.8% | Exchange-based | Noiri et al. 2022 |

| Readout fidelity | 97–99.5% | Spin-to-charge conversion + charge sensor | Noiri et al. 2022 |

| Gate time (1Q) | 50 ns – 1 μs | EDSR or ESR | — |

| Gate time (2Q) | 5–200 ns | Exchange pulse | — |

| Qubit pitch | ~80–150 nm | Gate-defined dot spacing | — |

| Operating temperature | 20 mK – 1 K | Hot-electron demonstrations at 1+ K | — |

| Connectivity | Nearest-neighbor | Exchange coupling between adjacent dots | — |

Scaling Considerations

- Qubit pitch of ~100 nm is orders of magnitude smaller than superconducting (~mm) or trapped-ion (~μm) qubits

- CMOS foundry compatibility enables potential mass production using existing semiconductor infrastructure

- Nearest-neighbor connectivity requires routing strategies for non-local gates

- Cryogenic CMOS control electronics co-integrated on-chip is an active research frontier

- Hot-qubit operation above 1 K would dramatically reduce cooling requirements

Extracted Figures

References

Original proposal

- D. Loss and D. P. DiVincenzo, “Quantum computation with quantum dots,” Phys. Rev. A 57, 120 (1998)

Single-qubit gates

- J. Yoneda et al., “A quantum-dot spin qubit with coherence limited by charge noise and fidelity higher than 99.9%,” Nat. Nanotechnol. 13, 102 (2018)

Two-qubit gates

- A. Noiri et al., “Fast universal quantum gate above the fault-tolerance threshold in silicon,” Nature 601, 338 (2022)

- X. Xue et al., “Quantum logic with spin qubits crossing the surface code threshold,” Nature 601, 343 (2022)

- A. R. Mills et al., “Two-qubit silicon quantum processor with operation fidelity exceeding 99%,” Sci. Adv. 8, eabn5130 (2022)

Multi-qubit processors

- S. G. J. Philips et al., “Universal control of a six-qubit quantum processor in silicon,” Nature 609, 919 (2022)

Reviews

- F. A. Zwanenburg et al., “Silicon quantum electronics,” Rev. Mod. Phys. 85, 961 (2013)

Linked Papers

Evergreen context

- divincenzo-criteria — this is the platform-level checklist that makes spin qubits legible across coherence, control, readout, and scalability at once

- spin-orbit-coupling-for-qubit-control — explains why modern devices favor electrically driven EDSR over local oscillating magnetic fields

- exchange-interaction-in-quantum-dots — the native nearest-neighbor coupling resource behind the gate family

Related Entries

- loss-divincenzo-qubit — detailed entry on the original proposal

- singlet-triplet-qubit — two-electron variant using singlet-triplet encoding

- exchange-only-qubit — three-electron all-exchange variant

- aeon-qubit — always-on exchange-only sweet-spot variant

- semiconductor-charge-qubit — charge-degree-of-freedom encoding

- kane-qubit — donor-based spin qubit in silicon